高速ADC/DAC电路及PCB设计要点整理

在高速模拟信号链设计中,印刷电路板(PCB)局布线需要考虑许多选项,有些选项比其它选项更重要,有些选项则取决于应用。最终的答案各不相同,但在所有情况下, 设计工程师都应兼顾全局,而不要过分计较布局布线的每一个细节。很多情况下做不到面面俱到,只能根据电路板及产品的面积进行取舍。

下面就给大家分享一下ADC/DAC电路及PCB设计中几个比较重要的问题:

1

数字地模拟地是否分割的问题

硬件工程师最常提出的问题是:使用ADC时是否应将接地层分为AGND和DGND接地层?

简单回答是:视情况而定。详细回答则是:通常不分离。为什么不呢?因为在大多数情况下,盲目分离接地层只会增加返回路径的电感,它所带来的坏处大于好处。

从公式V = L(di/dt)可以看出,破坏了GND的完整性,随着电感增加,电压噪声会提高。随着电感增加,设计人员一直努力压低的PDN阻抗也会增加。随着提高ADC采样速率的需求继续增长,降低开关电流(di/dt)的方式却很有限。因此,除非需要分离接地层,否则请保持这些接地连接。所以我们的结论是大部分情况下推荐不做DGND AGND分割,这个和大家早期经验做法相左。

我们大部分的产品是有尺寸要求的,可能没有足够和理想的空间。

受尺寸限制的影响,电路板无法实现良好的布局分割时,就需要分离接地层。这可能是为了符合传统设计要求或尺寸,必须将脏乱的总线电源或高噪声数字电路放在某些区域。这种情况下,分离接地层是实现良好性能的关键。然而,为使整体设计有效,必须在电路板的某个地方通过一个磁珠或局部连接点将这些接地层连在一起。

最终,PCB上往往会有一个连接点成为返回电流通过而不会导致性能降低或强行将返回电流耦合至敏感电路的最佳位置。如果此连接点位于转换器、其附近或下方,则不需要分离接地。

2

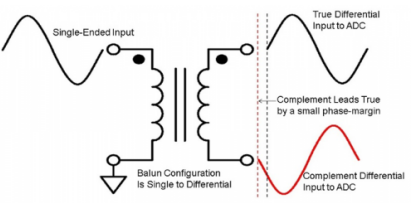

巴伦的选择问题,规格及类型

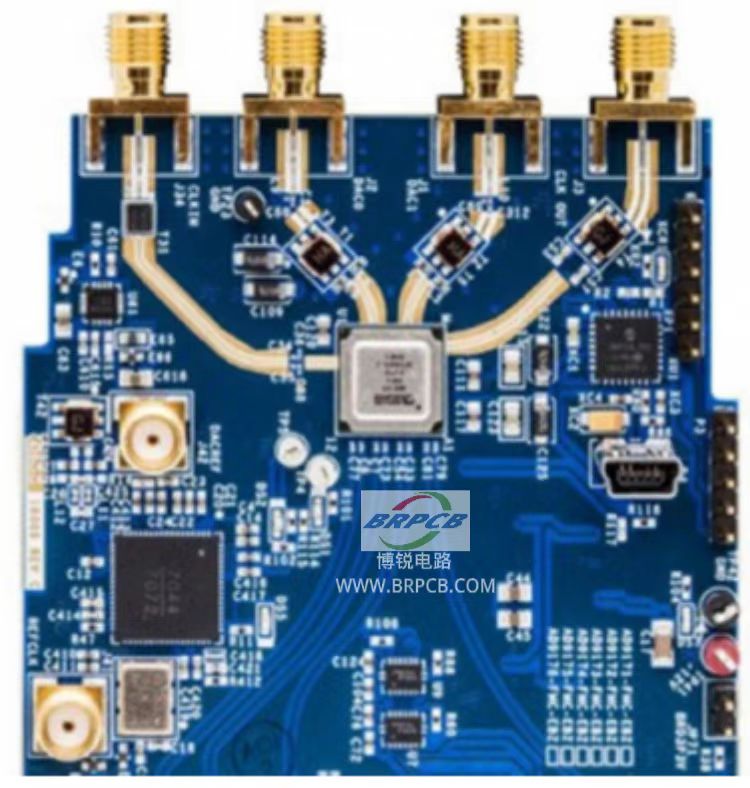

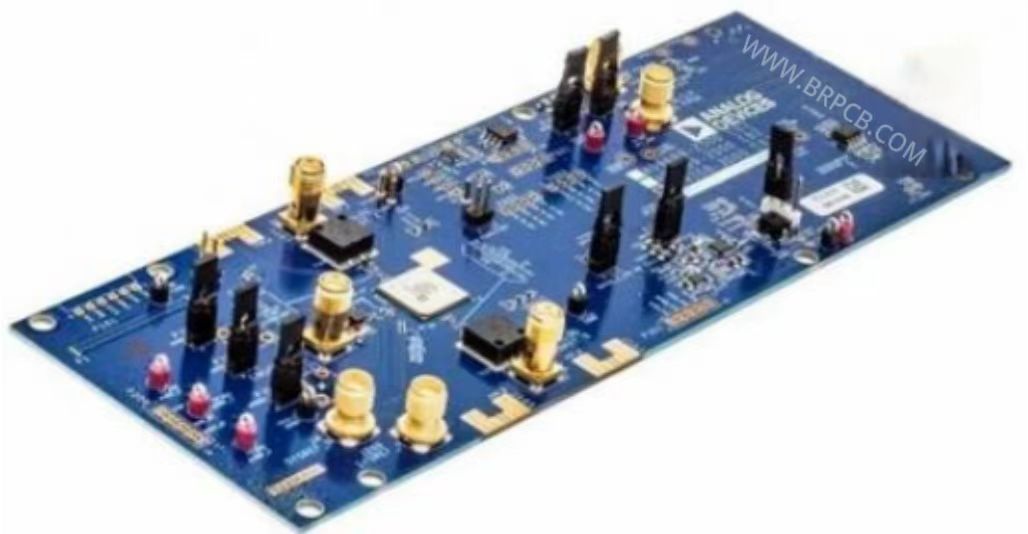

ADI的参考设计里面一般推荐是mini circuit的巴伦,但也有有高端的marki的巴伦变压器,动则上千元一个。

巴伦的选择主要考虑巴伦的阻抗变换比,相位一致性,幅度一致性,谐波等,当然如上所提,价格价格,我们永恒关注的。

3

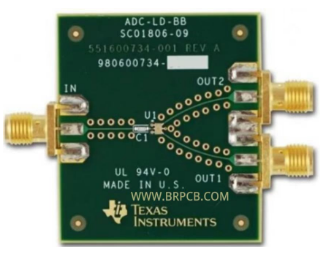

SMA接头选择问题

绝大多数ADC/DAC可以选择普通的SMA头,如果考虑3G以上性能,需要对SMA接入PCB进行匹配仿真或者更改更为高级的射频连接器,接头的匹配也是非常重要,直接影响信号的损耗。

4

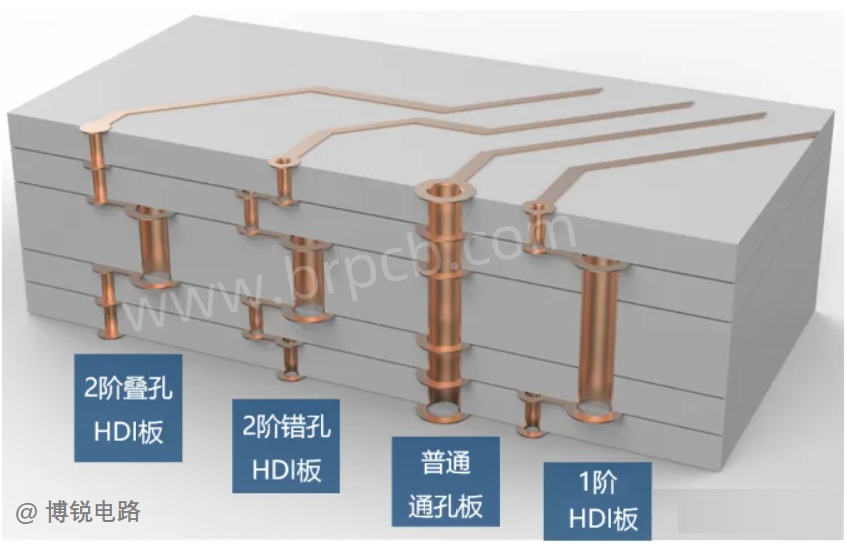

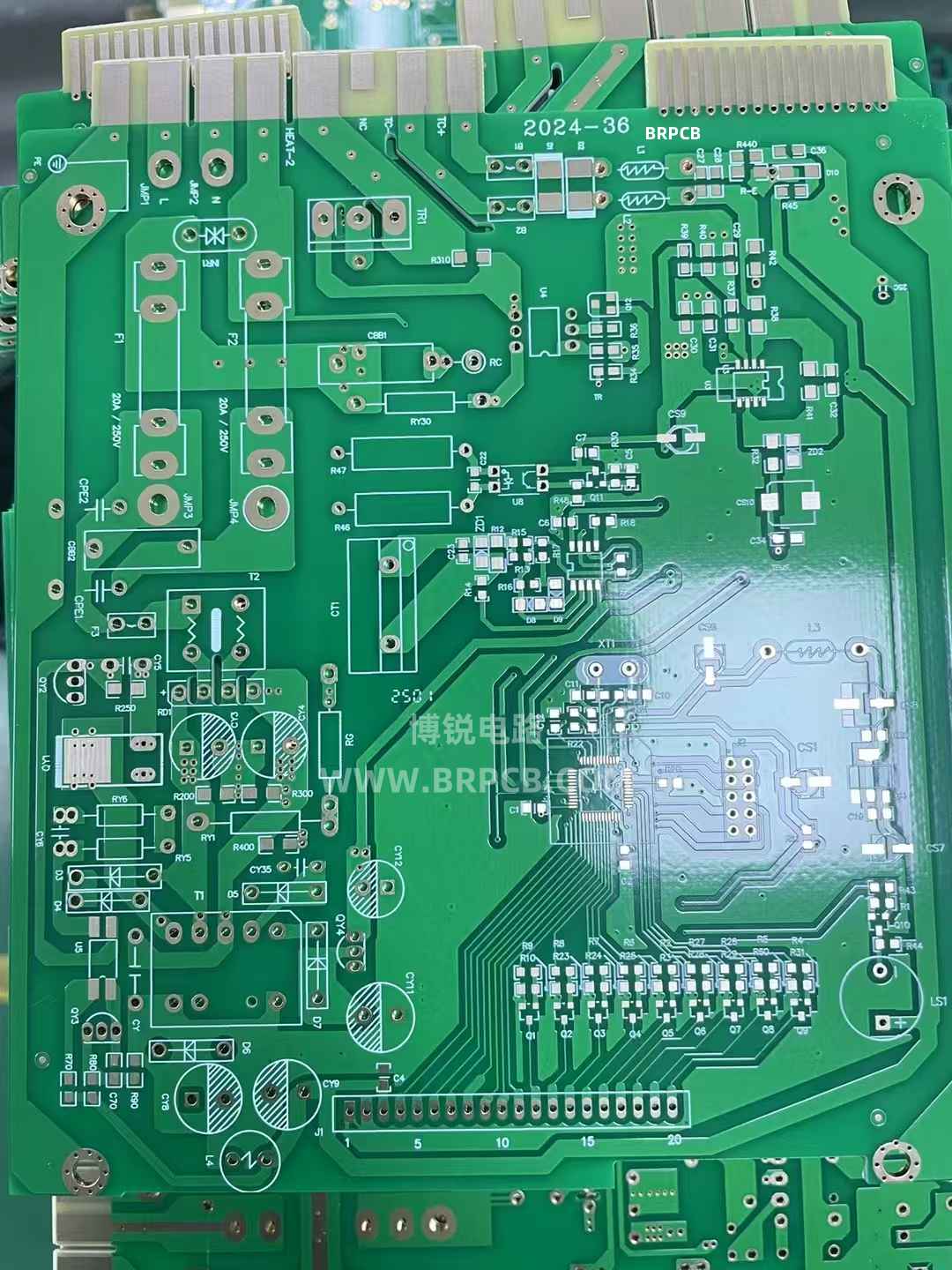

板材选择问题

我们大部分电路是采用传统的FR4板材,但是FR4板子具有插入损耗大,一致性稳定较差等原因,对应较高频率的ADC/DAC来讲,我们需要采用松下或者罗杰斯Rogers板材,以提高产品的性能。

5

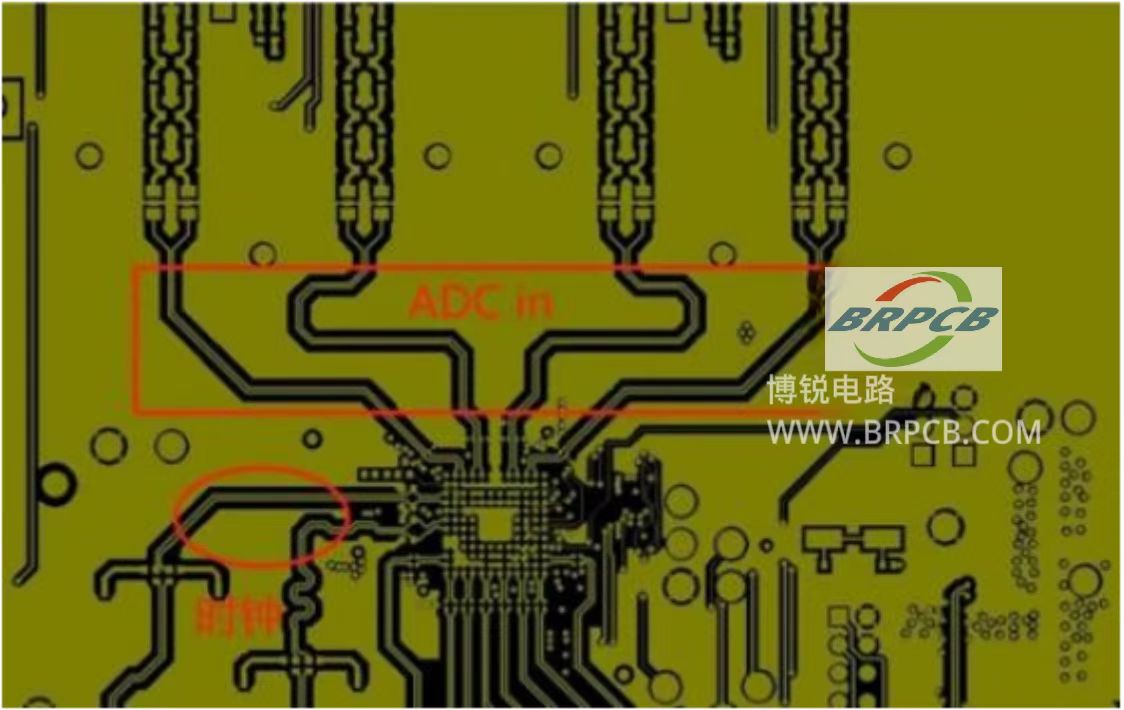

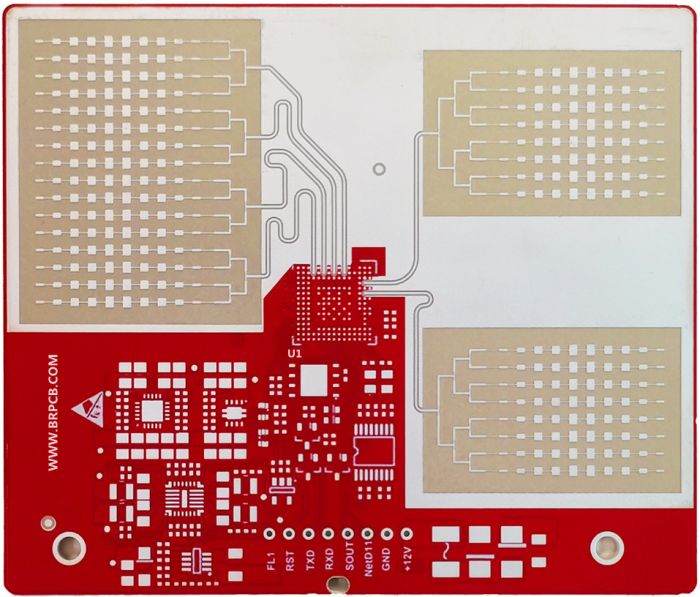

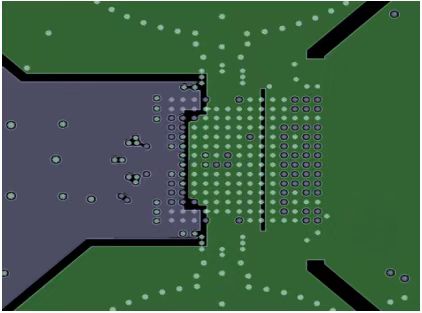

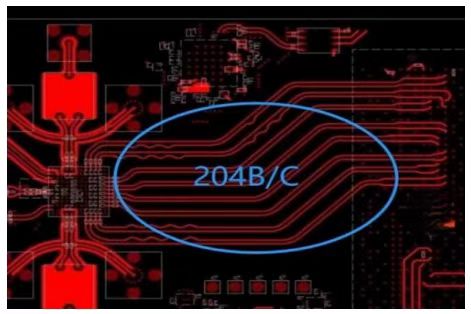

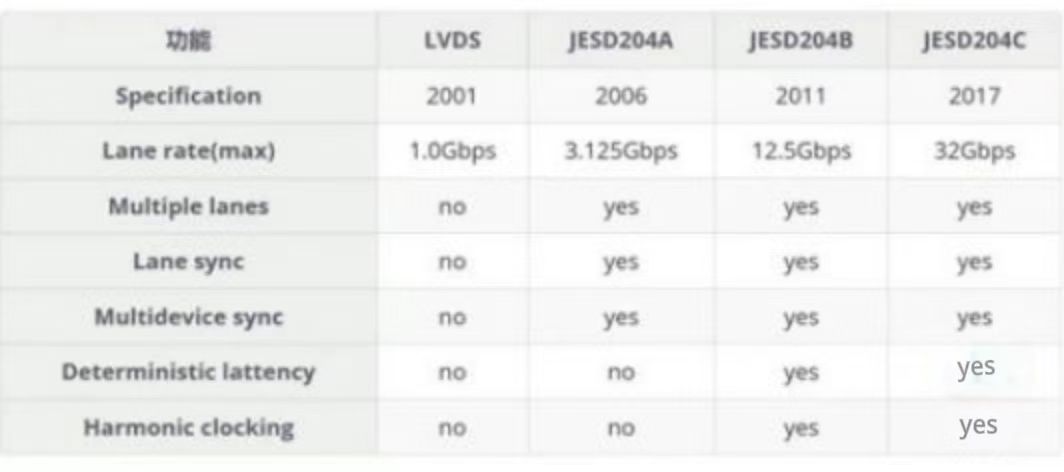

204B/204C高速走线

模拟世界和数字世界之间的联系离不开ADC和DAC。随着人们数据需求的增加、频谱资源的紧缺,许多行业的数据密集型应用持续突破模数数据交互的界限。高速ADC/DAC,以及适合处理大数据的FPGA平台逐渐被开发出来。用于大带宽、高速的模/数、数/模数据传输的JESD204协议也应运而生。协议目前有JESD204A、B、C几个不的同版本,相比传统的LVDS传输方式,其链路速率更高,同时也节约IO数量。

为了满足未来几年数据密集型应用更快处理数据的需求,JESD204C将多千兆位接口定义为数据转换器和逻辑器件之间必需的通信通道。高达32 GSPS的通道速率和64b/66b编码使超高带宽应用能以最小的开销来提高系统效率。这些和其他标准改进对于5G通信、雷达和电子战应用都大有裨益。

典型支持这些协议的芯片包括:AD9081、AD9082、AD9988、AD9986、AD9177

204C链路协议最高单通道已经高达32Gbps, 这就需要良好的高速设计经验甚至需要采用仿真优化走线,过孔来达到预期的性能。

6

隔离度的问题

随着芯片技术的发展和产品要求的提高,复杂产品对路数上的需要也是越来越多,再加上有限的紧张的空间,这就使得提高通道之间的隔离度变得困难,需要采用屏蔽等手段,且需要深厚的PCB设计经验和电磁场的知识。

7

时钟干扰的问题

在我们的经验中,经常会收到大家的反馈,就是ADC收到时钟的干扰,ADC采集到时钟,这就需要考虑如何从板级上提高时钟电路和各通道的隔离度。